| ||

|

RFワールド読者の掲示板Ⅱ

無線と高周波に関することを中心に、それ以外の話題も含めて、何でも書き込みOKの掲示板です。初めての方もネチケットを守って、お気軽にご参加下さい(^^)/

| ▼ | [RFW23]図6.12の減衰(1/2倍、1/4倍)回路 Hiroyuki Naito 19/4/26(金) 11:58 |

|

| Re:[RFW23]図6.12の減衰(1/2倍、1/4倍)回路 小池清之 19/4/27(土) 10:05 |

| Re:[RFW23]図6.12の減衰(1/2倍、1/4倍)回路 小池清之 19/4/27(土) 10:27 |

|

Hiroyuki Naito - 19/4/26(金) 11:58 - |

お世話になります。

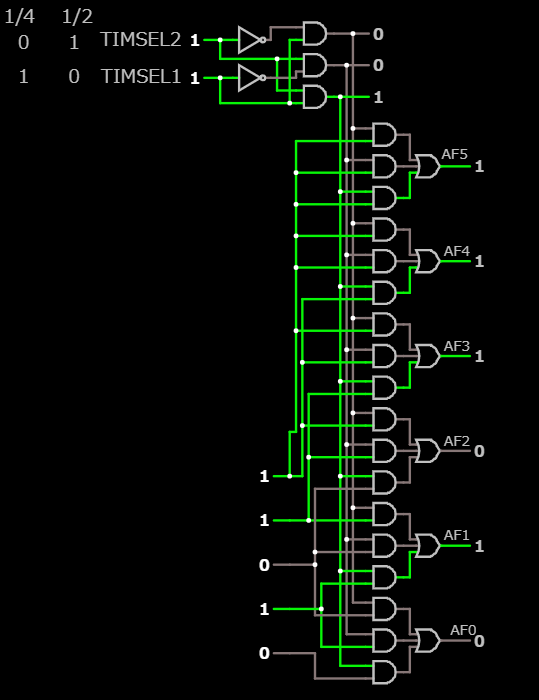

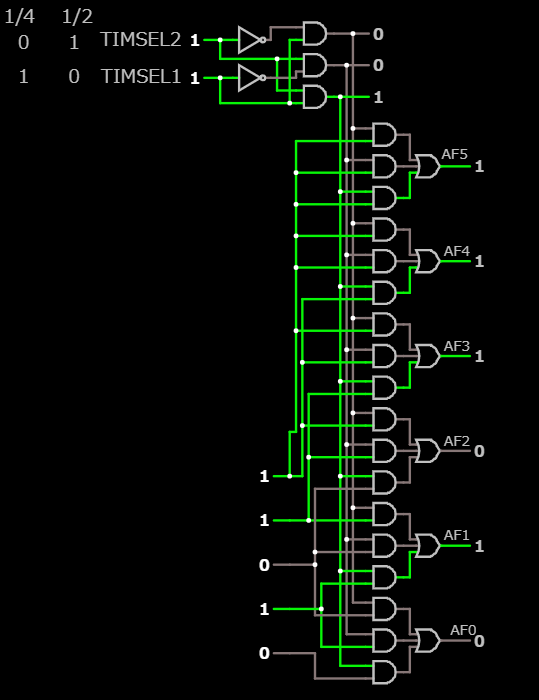

図6.12の減衰(1/2倍、1/4倍)回路をシミュレータで動作確認すると、

「絶対値処理した5ピット(正の値)を6ビットに拡張するときに、5ビットのMSB→6ビットのMSBとして、1/2倍あるいは1/4倍(1ビットあるいは2ビットシフト)して空いた上位ビットは先ほどのMSBで埋める」

という動作だと思うのですが、本文の説明では「負の数を2の補数で表しているとすると、~中略~ 符号ビットであるMSBの値を上に詰めながら桁をずらさないといけない」と説明されています。

絶対値処理された正の数と、2の補数表示の負数のシフト処理との関連がうまくつながりません。このあたりの考え方についてご教示をお願いいたします。

【648_図6_12の減衰回路.png : 27.3KB】

図6.12の減衰(1/2倍、1/4倍)回路をシミュレータで動作確認すると、

「絶対値処理した5ピット(正の値)を6ビットに拡張するときに、5ビットのMSB→6ビットのMSBとして、1/2倍あるいは1/4倍(1ビットあるいは2ビットシフト)して空いた上位ビットは先ほどのMSBで埋める」

という動作だと思うのですが、本文の説明では「負の数を2の補数で表しているとすると、~中略~ 符号ビットであるMSBの値を上に詰めながら桁をずらさないといけない」と説明されています。

絶対値処理された正の数と、2の補数表示の負数のシフト処理との関連がうまくつながりません。このあたりの考え方についてご教示をお願いいたします。

【648_図6_12の減衰回路.png : 27.3KB】

699 hits

|

小池清之 - 19/4/27(土) 10:05 - |

Hiroyuki Naito 様

ご質問ありがとうございます.

p.73では「絶対値処理回路」と「1/2回路,1/4回路」について,入力ビット数を図6.12の6ビットとは異なる5ビットで説明しています.その旨,本文中にも記述してあります.これは説明に用いる回路図のサイズを小さくしたかったからです.

このページでは本特集をパラパラと眺めた人が

●絶対値処理回路

●1/2回路,1/4回路

というところだけ気になって途中から読んだとしても誤解が無いように,汎用的な回路の説明にしています.これはどういう事かと言うと,「絶対値処理回路」では,入力5ビットに対して,出力は絶対値部分を表現している下4ビットを示している点,「1/2回路,1/4回路」では,負の値を考慮した回路としている点です.一方,図6.12ではこの回路全体が持つ事情があり,それが理解を妨げたのだと思われます.

図6.12では,「1/2回路,1/4回路」は絶対値回路の出力を受け取るので,負の値を考慮する必要はありません.MSBは常に"0"ですから,それを考慮すればセレクタに用いる論理素子を多数削除することができます.FPGAやCPLDではこうした無駄は容易に取り除けます.根元の端子を"L"に落とせば,最適化で削除されます.掲載した回路がそうなっていない理由は,教材として作ったからです.回路図を見て機能がわかるようにしたかったのです.

図6.12の「絶対値処理回路」はビットを増やしただけなのですが,その出力の取り出し方については説明不足でした.ここは,出力を取り出すときに「1/2」の値を取り出しています.

図6.13でいうとY1, Y2, Y3とC4(キャリー出力)に相当する部分を用いています.C4は符号に相当するビットですが,絶対値を得ているので常に"0"です.正確に言うと負の最大値が入ったときのみ"1"が立ちますが,入力となる周波数検波波形は図6.10のように,負の最大値まで振れません.

以上のことから,図6.12で右上の74HC283の1番ピンは常に"0"なので,その先で沢山枝分かれしているラインはすべて"0"を流しているだけです.上記1番ピンにつなぐ代わりにGNDに落としても構いませんし,経路を辿って論理素子を削除して行っても構いません.

図6.12のセレクタは2ビットの入力(TIMSEL1,TIMSEL2)で,0, 1/4, 1/2, 1 という倍率を切り替えますが,先ほど述べたようにセレクタの手前で1/2で取り出していますから,結果的に(TIMSEL1,TIMSEL2)で,0, 1/8, 1/4, 1/2 という倍率を切り替えています.このことはp.77の左下に記されています.

以上,ご質問の直接的なお答えではなく,前提や付帯条件を説明させていただきました.これを考慮して読んで頂ければ矛盾は無いと考えておりますがいかがでしょうか.

ご質問ありがとうございます.

p.73では「絶対値処理回路」と「1/2回路,1/4回路」について,入力ビット数を図6.12の6ビットとは異なる5ビットで説明しています.その旨,本文中にも記述してあります.これは説明に用いる回路図のサイズを小さくしたかったからです.

このページでは本特集をパラパラと眺めた人が

●絶対値処理回路

●1/2回路,1/4回路

というところだけ気になって途中から読んだとしても誤解が無いように,汎用的な回路の説明にしています.これはどういう事かと言うと,「絶対値処理回路」では,入力5ビットに対して,出力は絶対値部分を表現している下4ビットを示している点,「1/2回路,1/4回路」では,負の値を考慮した回路としている点です.一方,図6.12ではこの回路全体が持つ事情があり,それが理解を妨げたのだと思われます.

図6.12では,「1/2回路,1/4回路」は絶対値回路の出力を受け取るので,負の値を考慮する必要はありません.MSBは常に"0"ですから,それを考慮すればセレクタに用いる論理素子を多数削除することができます.FPGAやCPLDではこうした無駄は容易に取り除けます.根元の端子を"L"に落とせば,最適化で削除されます.掲載した回路がそうなっていない理由は,教材として作ったからです.回路図を見て機能がわかるようにしたかったのです.

図6.12の「絶対値処理回路」はビットを増やしただけなのですが,その出力の取り出し方については説明不足でした.ここは,出力を取り出すときに「1/2」の値を取り出しています.

図6.13でいうとY1, Y2, Y3とC4(キャリー出力)に相当する部分を用いています.C4は符号に相当するビットですが,絶対値を得ているので常に"0"です.正確に言うと負の最大値が入ったときのみ"1"が立ちますが,入力となる周波数検波波形は図6.10のように,負の最大値まで振れません.

以上のことから,図6.12で右上の74HC283の1番ピンは常に"0"なので,その先で沢山枝分かれしているラインはすべて"0"を流しているだけです.上記1番ピンにつなぐ代わりにGNDに落としても構いませんし,経路を辿って論理素子を削除して行っても構いません.

図6.12のセレクタは2ビットの入力(TIMSEL1,TIMSEL2)で,0, 1/4, 1/2, 1 という倍率を切り替えますが,先ほど述べたようにセレクタの手前で1/2で取り出していますから,結果的に(TIMSEL1,TIMSEL2)で,0, 1/8, 1/4, 1/2 という倍率を切り替えています.このことはp.77の左下に記されています.

以上,ご質問の直接的なお答えではなく,前提や付帯条件を説明させていただきました.これを考慮して読んで頂ければ矛盾は無いと考えておりますがいかがでしょうか.

799 hits

|

小池清之 - 19/4/27(土) 10:27 - |

訂正

誤:負の最大値

正:負の値で振幅最大というつもりでした.最小値ですね.

失礼しました.

誤:負の最大値

正:負の値で振幅最大というつもりでした.最小値ですね.

失礼しました.

790 hits

60,725