| ||

|

RFワールド読者の掲示板Ⅱ

無線と高周波に関することを中心に、それ以外の話題も含めて、何でも書き込みOKの掲示板です。初めての方もネチケットを守って、お気軽にご参加下さい(^^)/

|

Hiroyuki Naito - 19/4/26(金) 11:58 - |

お世話になります。

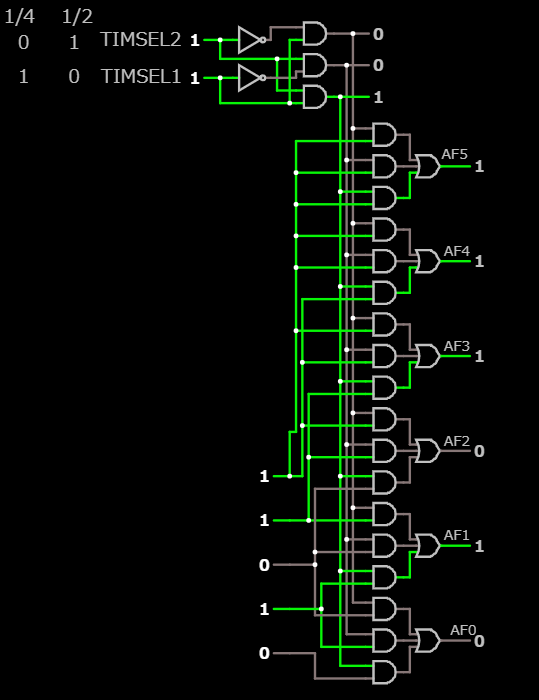

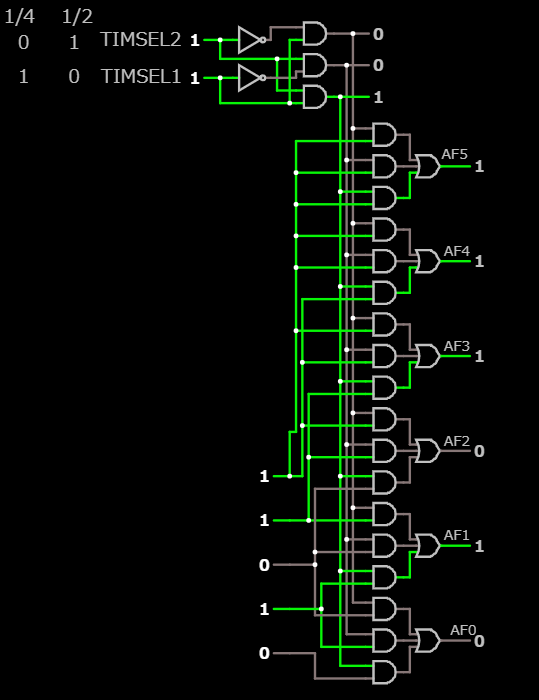

図6.12の減衰(1/2倍、1/4倍)回路をシミュレータで動作確認すると、

「絶対値処理した5ピット(正の値)を6ビットに拡張するときに、5ビットのMSB→6ビットのMSBとして、1/2倍あるいは1/4倍(1ビットあるいは2ビットシフト)して空いた上位ビットは先ほどのMSBで埋める」

という動作だと思うのですが、本文の説明では「負の数を2の補数で表しているとすると、~中略~ 符号ビットであるMSBの値を上に詰めながら桁をずらさないといけない」と説明されています。

絶対値処理された正の数と、2の補数表示の負数のシフト処理との関連がうまくつながりません。このあたりの考え方についてご教示をお願いいたします。

【648_図6_12の減衰回路.png : 27.3KB】

図6.12の減衰(1/2倍、1/4倍)回路をシミュレータで動作確認すると、

「絶対値処理した5ピット(正の値)を6ビットに拡張するときに、5ビットのMSB→6ビットのMSBとして、1/2倍あるいは1/4倍(1ビットあるいは2ビットシフト)して空いた上位ビットは先ほどのMSBで埋める」

という動作だと思うのですが、本文の説明では「負の数を2の補数で表しているとすると、~中略~ 符号ビットであるMSBの値を上に詰めながら桁をずらさないといけない」と説明されています。

絶対値処理された正の数と、2の補数表示の負数のシフト処理との関連がうまくつながりません。このあたりの考え方についてご教示をお願いいたします。

【648_図6_12の減衰回路.png : 27.3KB】

617 hits

| ▼ | [RFW23]図6.12の減衰(1/2倍、1/4倍)回路 Hiroyuki Naito 19/4/26(金) 11:58 |

|

| Re:[RFW23]図6.12の減衰(1/2倍、1/4倍)回路 小池清之 19/4/27(土) 10:05 |

| Re:[RFW23]図6.12の減衰(1/2倍、1/4倍)回路 小池清之 19/4/27(土) 10:27 |

57,177