| ||

|

RFワールド読者の掲示板Ⅱ

無線と高周波に関することを中心に、それ以外の話題も含めて、何でも書き込みOKの掲示板です。初めての方もネチケットを守って、お気軽にご参加下さい(^^)/

| ▼ | [RFW23]図6_3シフトクロック発生回路 Hiroyuki Naito 19/2/12(火) 17:19 |

|

| Re:[RFW23]図6_3シフトクロック発生回路 Hiroyuki Naito 19/2/15(金) 16:29 |

|

| Re:[RFW23]図6_3シフトクロック発生回路 小池清之 19/2/26(火) 0:40 |

|

|

Hiroyuki Naito - 19/2/15(金) 16:29 - |

▼editorさん、小池先生:

いつも丁寧なご回答をありがとうございます。

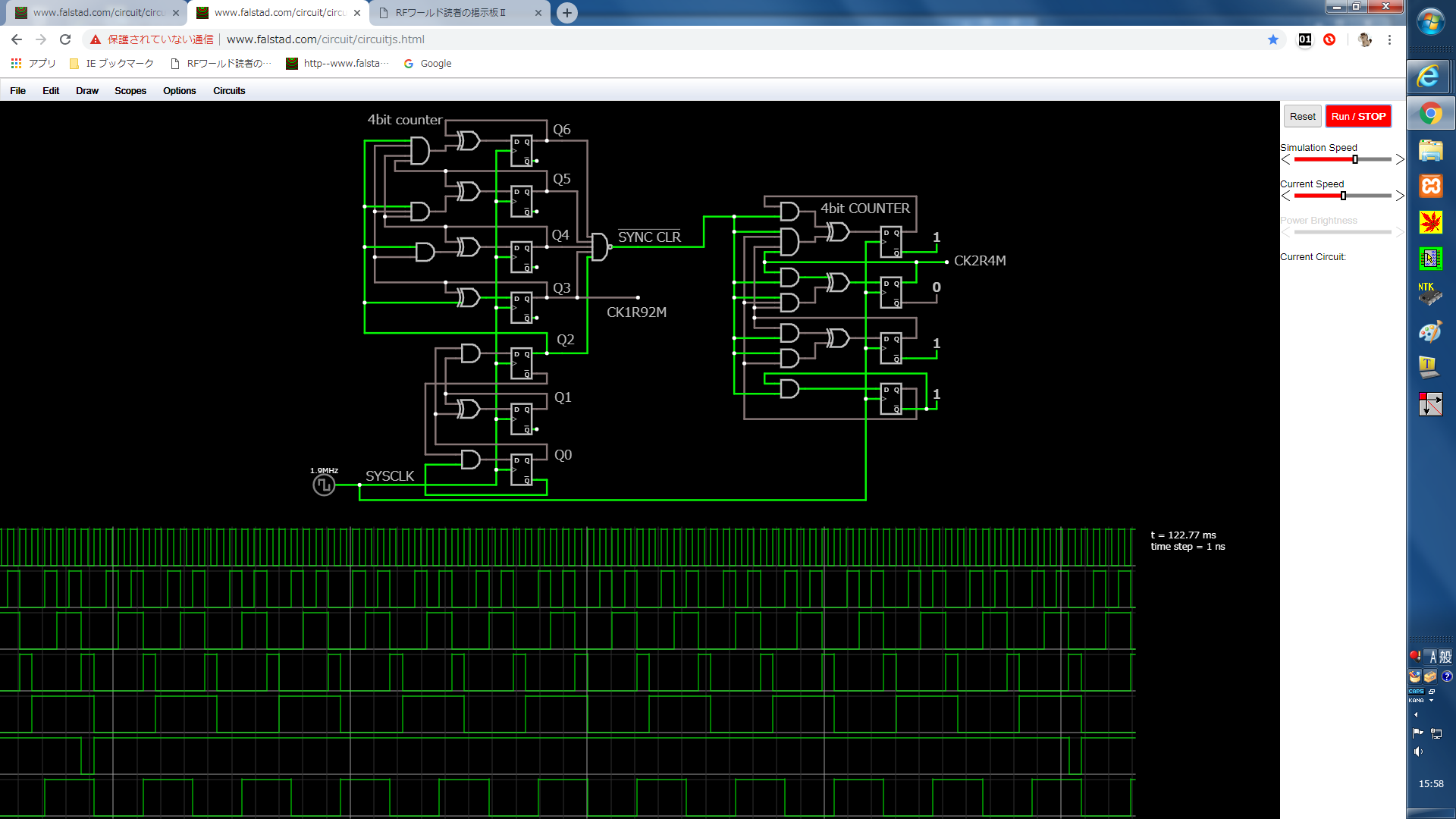

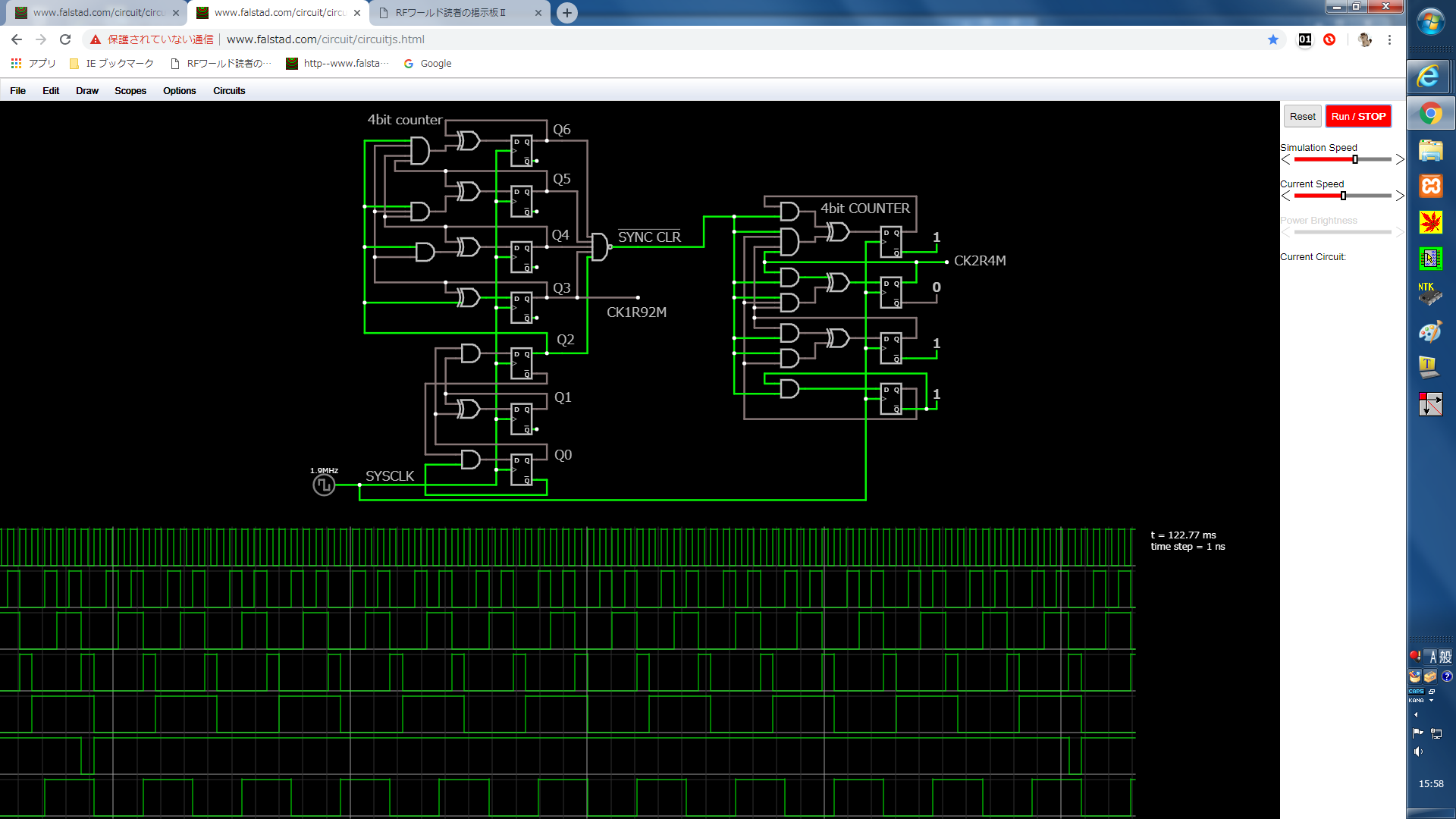

図6.3のシフトクロック回路の~(SYNC CLR)信号を、図5.14の4bitフリーランカウンタの~(SYNC CLR)に接続して、図6.5の二つのシフトクロック:CK1R92MとCK2R4Mの立上りエッジが一致しないことを確認できました。

添付のタイムチャートの下から3番目…CK1R92M

添付のタイムチャートの下から2番目…~(SYNC CLR)

添付のタイムチャートの一番下…CK2R4M

このような工夫が具体的にどんなメリットをもたらすのかはまだ想像できませんが、二つの信号のタイミングを決して一致させたくない場面はありそうな気はします。

【618_図6_5二つのシフトクロックの立上りエッジ.png : 260.3KB】

いつも丁寧なご回答をありがとうございます。

図6.3のシフトクロック回路の~(SYNC CLR)信号を、図5.14の4bitフリーランカウンタの~(SYNC CLR)に接続して、図6.5の二つのシフトクロック:CK1R92MとCK2R4Mの立上りエッジが一致しないことを確認できました。

添付のタイムチャートの下から3番目…CK1R92M

添付のタイムチャートの下から2番目…~(SYNC CLR)

添付のタイムチャートの一番下…CK2R4M

このような工夫が具体的にどんなメリットをもたらすのかはまだ想像できませんが、二つの信号のタイミングを決して一致させたくない場面はありそうな気はします。

【618_図6_5二つのシフトクロックの立上りエッジ.png : 260.3KB】

602 hits

|

小池清之

|

▼Hiroyuki Naitoさん:

いつも詳細なご検討のご報告,誠にありがとうございます.

>このような工夫が具体的にどんなメリットをもたらすのかはまだ想像できませんが、二つの信号のタイミングを決して一致させたくない場面はありそうな気はします。

この2系統のクロックに対する工夫は,実はこの回路ではあまり役に立っていません.これはサンプルレート変換用のクロックです.サンプルレート変換は,RFW23で紹介した回路の前段階に別の検討をしておりましてその名残りとなっています.先に検討していた方式は次のようなものでした.

その方法とは,2.4MHzで流れてくる位相情報を変換後の1.92MHzに変換する際,1.92MHzのクロック立ち上がりが,2.4MHzクロック立ち上がり間のどの位置にあるかで,位相の重み付け加算を行うものでした.言葉だとわかりづらいので,添付の図をご覧ください.

このm,nの組み合わせを指定しやすくするため,このようなクロック生成方式にしました.2.4MHzと1.92MHzのもとになっている19.2MHzクロックの,80クロック周期の中の状態として指定できるというわけです.

この方式は頭の中で考えている間はとても良い方式に思えましたが,実際に作ってみると回路規模の割に性能改善はわずかでした.そこでRFW23のような回路に落ち着いたというわけなのです.

【626_重み付け加算式サンプルレート変換.gif : 45.1KB】

いつも詳細なご検討のご報告,誠にありがとうございます.

>このような工夫が具体的にどんなメリットをもたらすのかはまだ想像できませんが、二つの信号のタイミングを決して一致させたくない場面はありそうな気はします。

この2系統のクロックに対する工夫は,実はこの回路ではあまり役に立っていません.これはサンプルレート変換用のクロックです.サンプルレート変換は,RFW23で紹介した回路の前段階に別の検討をしておりましてその名残りとなっています.先に検討していた方式は次のようなものでした.

その方法とは,2.4MHzで流れてくる位相情報を変換後の1.92MHzに変換する際,1.92MHzのクロック立ち上がりが,2.4MHzクロック立ち上がり間のどの位置にあるかで,位相の重み付け加算を行うものでした.言葉だとわかりづらいので,添付の図をご覧ください.

このm,nの組み合わせを指定しやすくするため,このようなクロック生成方式にしました.2.4MHzと1.92MHzのもとになっている19.2MHzクロックの,80クロック周期の中の状態として指定できるというわけです.

この方式は頭の中で考えている間はとても良い方式に思えましたが,実際に作ってみると回路規模の割に性能改善はわずかでした.そこでRFW23のような回路に落ち着いたというわけなのです.

【626_重み付け加算式サンプルレート変換.gif : 45.1KB】

634 hits

57,211