| ||

|

RFワールド読者の掲示板Ⅱ

無線と高周波に関することを中心に、それ以外の話題も含めて、何でも書き込みOKの掲示板です。初めての方もネチケットを守って、お気軽にご参加下さい(^^)/

| ▼ | [RFW41] 4章 SPIモジュールの動作確認 Hiroyuki Naito 18/10/5(金) 16:27 |

|

| Re:[RFW41] 4章 SPIモジュールの動作確認 森榮 18/10/6(土) 13:20 |

| Re:[RFW41] 4章 SPIモジュールの動作確認 Hiroyuki Naito 18/11/27(火) 17:49 |

|

| Re:[RFW41] 4章 SPIモジュールの動作確認 森榮 18/11/27(火) 20:37 |

|

Hiroyuki Naito - 18/10/5(金) 16:27 - |

500 hits

|

森榮 - 18/10/6(土) 13:20 - |

Hiroyuki Naito 様

記事の内容を再現して実験くださいまして、

大変感謝いたします。

SignalTapIIはレコード長の上限があることが難点でございます。

Power-Upトリガと使って、かつ、クロックを80MHzでモニタされているようでしたら、

少し、Verilogコードを改変してみるのはいかがでしょうか?

公開のソースコードでは、100mSおきに各レジスタ書き込みを送っていますが、

これを10mSおきになるようにVerilogコードを変更すると、全てのレジスタ設定をモニタすることが出来ます。

(100mSおき → 10mSおき のVerilogコード変更に間違いがないことが条件でございますが。。)

▼Hiroyuki Naitoさん:

>お世話になります。

>

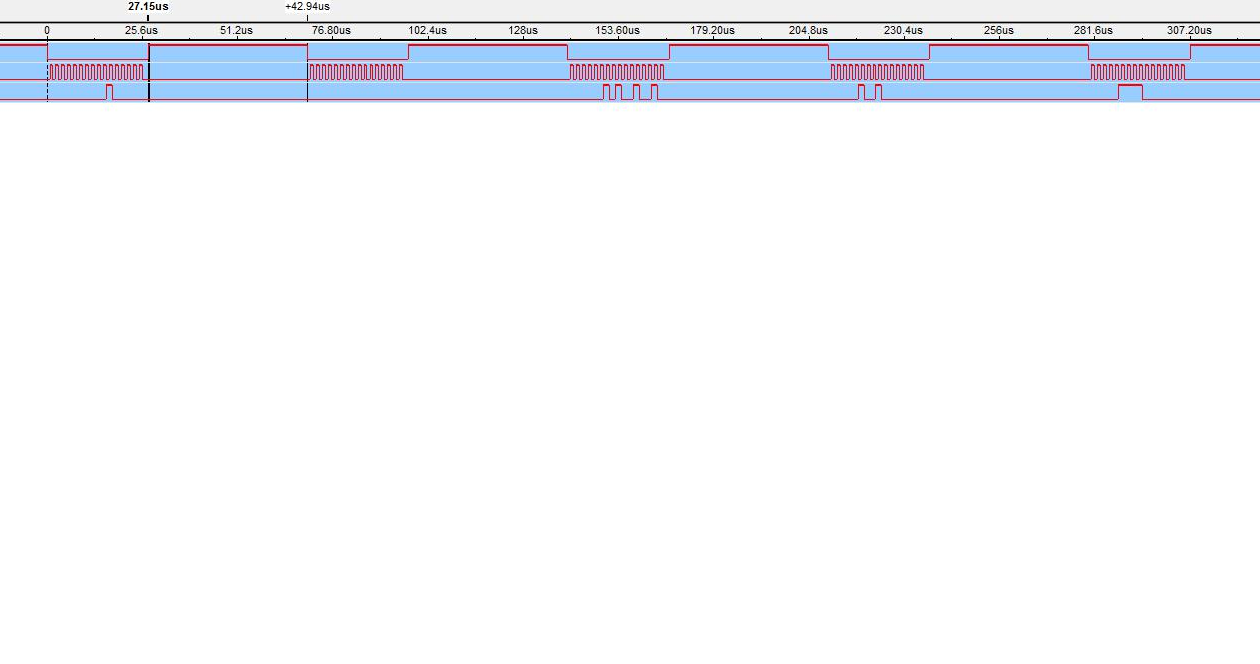

>P46で「SPIモジュールの動作確認は、読者の創意工夫でおこなう」ということ

>でしたので、SignalTap IIのPower-Upトリガを使ってCS、SPCK、SDIの信号を

>捉えてみました(添付参照)。

>

>表4.1の5ヶの設定のうち、1番目の設定が捉えられたようです(クロックはclk80m)。

>RAMを最大の128kにしても2番目以降の設定データは見ることができませんでしたが、

>何か別の方法で見ることはできるのでしょうか。

>

>※Qauartus IIはV13.0(32bit)を使用しています。

記事の内容を再現して実験くださいまして、

大変感謝いたします。

SignalTapIIはレコード長の上限があることが難点でございます。

Power-Upトリガと使って、かつ、クロックを80MHzでモニタされているようでしたら、

少し、Verilogコードを改変してみるのはいかがでしょうか?

公開のソースコードでは、100mSおきに各レジスタ書き込みを送っていますが、

これを10mSおきになるようにVerilogコードを変更すると、全てのレジスタ設定をモニタすることが出来ます。

(100mSおき → 10mSおき のVerilogコード変更に間違いがないことが条件でございますが。。)

▼Hiroyuki Naitoさん:

>お世話になります。

>

>P46で「SPIモジュールの動作確認は、読者の創意工夫でおこなう」ということ

>でしたので、SignalTap IIのPower-Upトリガを使ってCS、SPCK、SDIの信号を

>捉えてみました(添付参照)。

>

>表4.1の5ヶの設定のうち、1番目の設定が捉えられたようです(クロックはclk80m)。

>RAMを最大の128kにしても2番目以降の設定データは見ることができませんでしたが、

>何か別の方法で見ることはできるのでしょうか。

>

>※Qauartus IIはV13.0(32bit)を使用しています。

508 hits

|

Hiroyuki Naito - 18/11/27(火) 17:49 - |

▼森榮さん:

>公開のソースコードでは、100mSおきに各レジスタ書き込みを送っていますが、

>これを10mSおきになるようにVerilogコードを変更すると、全てのレジスタ設定をモニタすることが出来ます。

>(100mSおき → 10mSおき のVerilogコード変更に間違いがないことが条件でございますが。。)

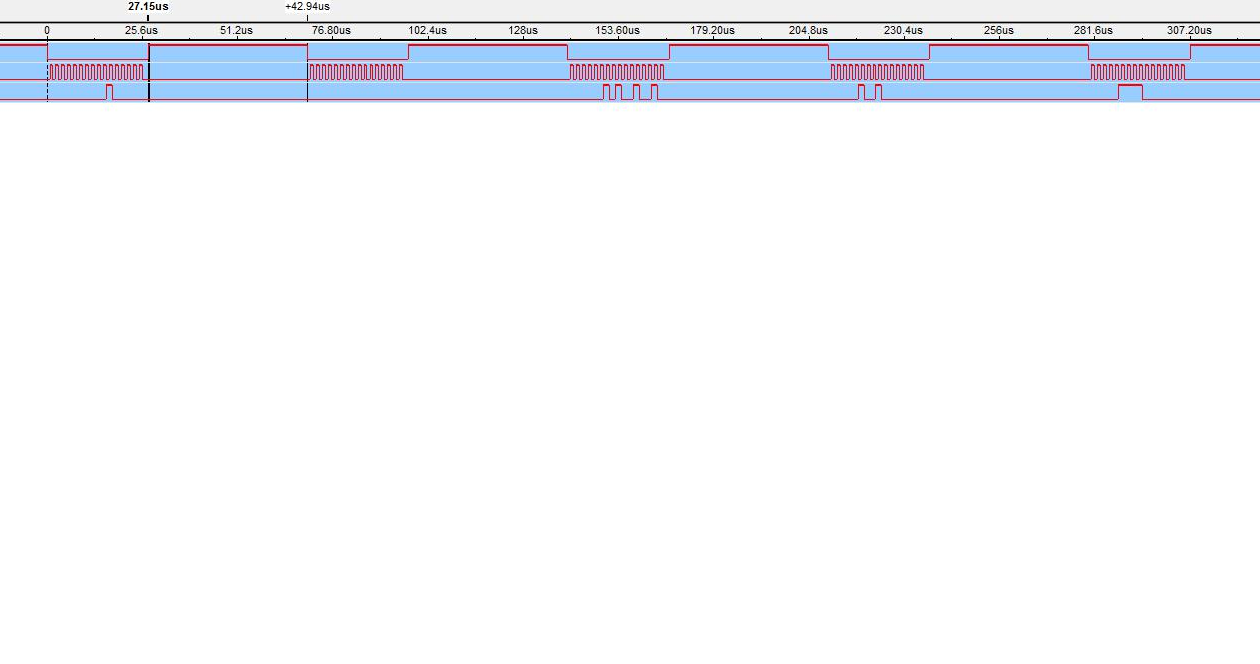

お世話になります。アドバイス有難うございました。

128kBの最大レコード長でも1.43msしかモニタできませんでしたので、設定データと

データの間隔を70usくらいに縮めてみました。

添付がその結果ですが、0x0020→0x0000→0x0292→0x0480→0x0780の5ヶのデータを

捉えることができました。

【579_dac_init.png : 86.4KB】

>公開のソースコードでは、100mSおきに各レジスタ書き込みを送っていますが、

>これを10mSおきになるようにVerilogコードを変更すると、全てのレジスタ設定をモニタすることが出来ます。

>(100mSおき → 10mSおき のVerilogコード変更に間違いがないことが条件でございますが。。)

お世話になります。アドバイス有難うございました。

128kBの最大レコード長でも1.43msしかモニタできませんでしたので、設定データと

データの間隔を70usくらいに縮めてみました。

添付がその結果ですが、0x0020→0x0000→0x0292→0x0480→0x0780の5ヶのデータを

捉えることができました。

【579_dac_init.png : 86.4KB】

503 hits

|

森榮 - 18/11/27(火) 20:37 - |

▼Hiroyuki Naitoさん:

>▼森榮さん:

>

>>公開のソースコードでは、100mSおきに各レジスタ書き込みを送っていますが、

>>これを10mSおきになるようにVerilogコードを変更すると、全てのレジスタ設定をモニタすることが出来ます。

>>(100mSおき → 10mSおき のVerilogコード変更に間違いがないことが条件でございますが。。)

>

>お世話になります。アドバイス有難うございました。

>

>128kBの最大レコード長でも1.43msしかモニタできませんでしたので、設定データと

>データの間隔を70usくらいに縮めてみました。

>

>添付がその結果ですが、0x0020→0x0000→0x0292→0x0480→0x0780の5ヶのデータを

>捉えることができました。

頒布基板をご活用くださいまして、誠に有難うございます。

データ間隔を、約70uSまで縮めて観測された結果を拝見させていただきました。

SPIデータ設定は、正しく出来ているかと思います。

他には、このような方法もございます。

SPI送信をFPGA初期化後5秒後など遅めにして、なおかつ、観測したいアドレスへの設定箇所でトリガを出して、SignalTapに取り込む、といった方法などがございます。もし宜しければ、お試しください。

宜しくお願い致します。

>▼森榮さん:

>

>>公開のソースコードでは、100mSおきに各レジスタ書き込みを送っていますが、

>>これを10mSおきになるようにVerilogコードを変更すると、全てのレジスタ設定をモニタすることが出来ます。

>>(100mSおき → 10mSおき のVerilogコード変更に間違いがないことが条件でございますが。。)

>

>お世話になります。アドバイス有難うございました。

>

>128kBの最大レコード長でも1.43msしかモニタできませんでしたので、設定データと

>データの間隔を70usくらいに縮めてみました。

>

>添付がその結果ですが、0x0020→0x0000→0x0292→0x0480→0x0780の5ヶのデータを

>捉えることができました。

頒布基板をご活用くださいまして、誠に有難うございます。

データ間隔を、約70uSまで縮めて観測された結果を拝見させていただきました。

SPIデータ設定は、正しく出来ているかと思います。

他には、このような方法もございます。

SPI送信をFPGA初期化後5秒後など遅めにして、なおかつ、観測したいアドレスへの設定箇所でトリガを出して、SignalTapに取り込む、といった方法などがございます。もし宜しければ、お試しください。

宜しくお願い致します。

526 hits

57,181